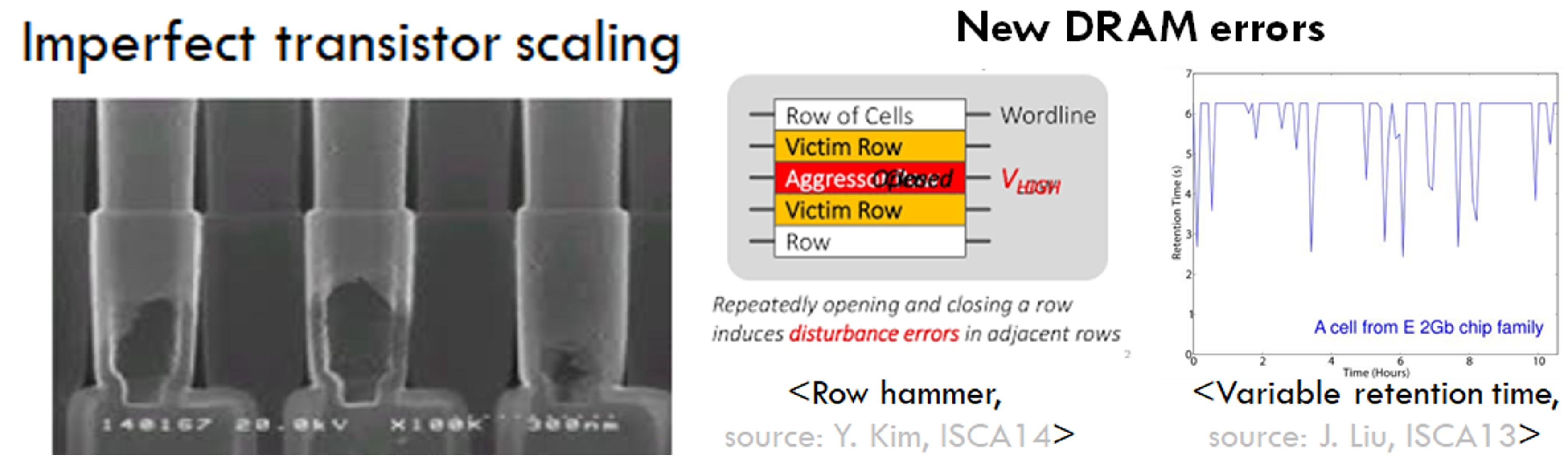

As processing scaling continues, transistors became more vulnerable to faults and errors. In memories, there are new types of errors, such as variable retention time and row hammer. In logics, increasing variability makes it more difficult to exploit faster transistors from the scaling: with fewer atoms to build a transistor, few more atoms now greatly affect the performance of the transistor. Because of this process variation, there has to be more timing margins to run safe.

The goal of this research is to protect memories and logics against these growing errors. This includes applying stronger error correcting codes (ECC) to protect data in memories, and predicting logic errors from aggressive dynamic voltage/frequency scaling (DVFS).

(Korean) 공정이 세밀화되면서 트랜지스터는 불량과 에러들에 더 취약해지고 있다. 메모리에서는 variable retention time과 row hammer와 같은 새로운 유형의 에러들이 발생하고 있고, 시스템반도체에서는 증가하는 변동성으로 공정 세밀화로 얻어질 수 있는 성능 개선을 어렵게 만들고 있다: 공정 세밀화로 점점 더 적은 원자들로 트랜지스터를 구성하면서, 몇개의 원자들만 더 붙어도 성능에 큰 변화가 발생할 수 있고, 이를 고려하여 설계에는 보수적으로 동작속도를 잡는다.

이 연구의 목표는 메모리와 시스템반도체를 이렇게 증가하는 에러들로부터 보호하는 것이다. 세부 연구 주제로는 메모리 데이터를 보호하기 위한 더 강력한 error correcting codes (ECC)와 dynamic voltage/frequency scaling(DVFS)를 공격적으로 적용하기 위하여 발생할 수 있는 로직 에러들을 예측하는 것 등이 있다.